存算一体芯片:AI时代的最佳答案?

近日,存算一体(存内计算)芯片设计公司苹芯科技宣布于数月前完成千万级美元A轮融资。中国工程院院士邬贺铨在2022中国算力大会上表示,对自动驾驶等场景产生的热数据(实时性数据),存算分离会使数据在存储和计算之间来回输入,此时存内计算更适合热数据的处理。

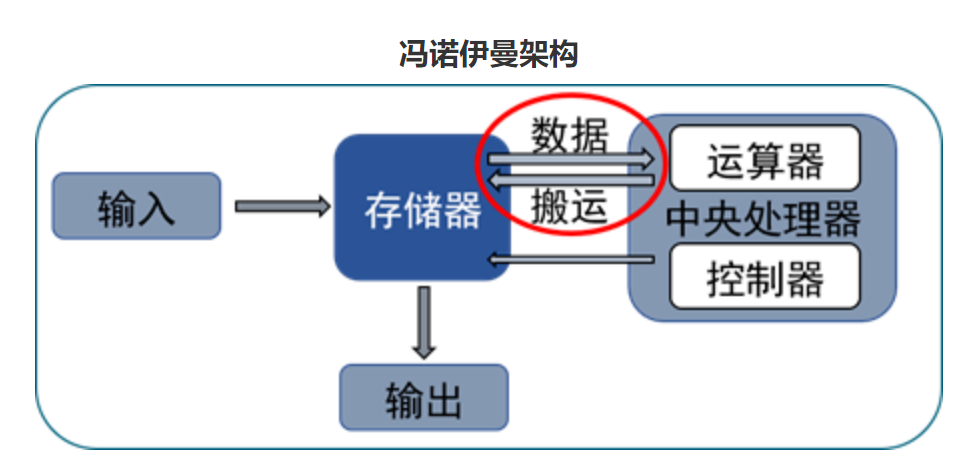

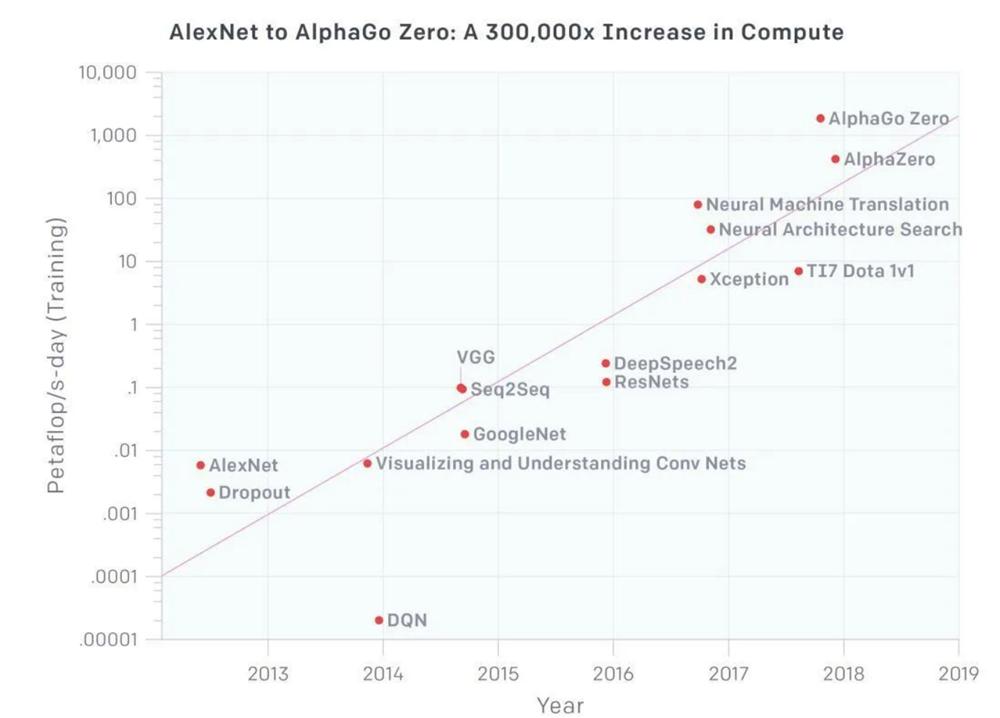

在冯诺依曼架构中,计算和存储功能分别由中央处理器和存储器完成。而处理器在跟随摩尔定律逐年提升性能的过程中,将对制程工艺不敏感的存储器甩在了后面,两者的性能差距形成了“存储墙”。相比之下,存算一体能够避免数据来回搬运所造成的功耗损失和时间延迟。在AI技术不断释放数据洪流和算力场景需求的大趋势下,存算一体芯片越来越受到产业界和资本市场的关注。

来源:《中国科学:信息科学》

来源:《中国科学:信息科学》

绕过存储墙是AI时代刚需

早在1969年,斯坦福研究所的William Kautz就提出了存算一体的概念。Kautz提出在芯片的存储单元中加入逻辑电路,并将多个单元连接起来组成阵列,这样能够打造更加灵活、速度更快、耗能更低的数字电路,以更好地适应当时大规模集成电路的需求。然而,早期的存算一体研究并没有取得明显的突破,以冯诺依曼架构为蓝本、按照摩尔定律的步伐提升芯片性能,逐渐成为产业界的共识。

但近几年来,存算一体又回到了业界的视野,并被视为重要的技术方向。

知存科技创始人兼CEO王绍迪向《中国电子报》指出,过去几十年是摩尔定律快速发展的时期,加上开发新的架构需要高昂的投入,因此在摩尔定律还能往下走的时候,产业界对存算一体这类架构创新的需求还不高。但近十年以来,算力需求的增长使存储墙的问题越来越凸显。

“到2010年以后进入后摩尔时代,行业内日益增长的算力需求和几乎走到极限的摩尔定律之间越来越突出的矛盾已经成为人工智能发展的巨大瓶颈。因此,能解决存储墙问题的存算一体技术受到了越来越多的关注,近几年在产业界得到了非常快速的发展。”王绍迪说。

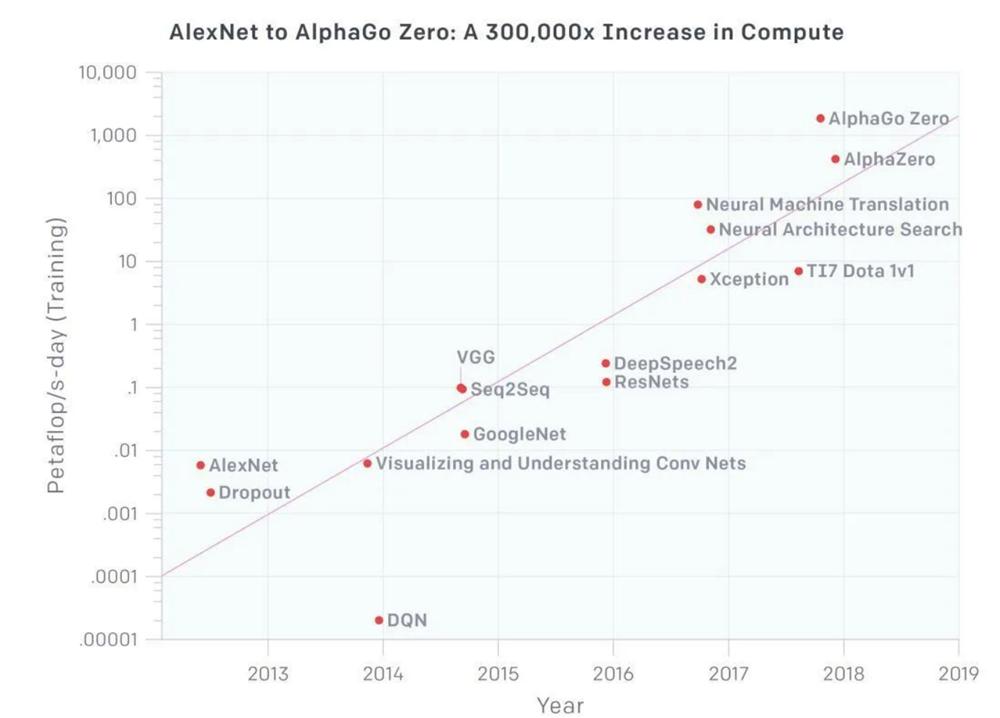

尤其在2016年人工智能Alpha Go在围棋对弈中战胜世界冠军李世石之后,以深度学习为代表的统计学习理论与方法促动了整个人工智能行业的发展。OpenAI的分析显示,自 2012 年以来,人工智能训练任务中使用的算力每 3.5 个月翻一倍。计算需求的突飞猛进,对算力芯片的效能提出了更高的要求和新的挑战。

从2013到2019年AI算力实现了30万倍的提升

来源:OpenAI

来源:OpenAI

九天睿芯董事长兼CEO刘洪杰向《中国电子报》表示,在冯诺依曼架构中,处理器从处理单元外的存储器提取数据,搬运时间往往是运算时间的成百上千倍。

“深度学习加速的最大挑战就是数据在计算单元和存储单元之间频繁的移动,市场急需可实现超高能效并且可以快速迭代的智能计算芯片来满足日新月异的市场变化。我们推出的新型类脑计算的存内计算体系架构就是面向AI发展的算力瓶颈,核心技术是解决AI算力能效比偏低的核心刚性需求。算力堆叠带来能耗问题,存算一体就是很好的解决方案。”刘洪杰说。

多种技术架构待产学研共同探索

面向智能化时代的算力需求和计算服务业态变革,英特尔、三星等IDM厂商和新锐的算力芯片厂商都在探索存算一体芯片,并衍生出不同的架构和技术路线。

刘洪杰表示,目前全球存算一体仍处于蓬勃发展阶段,没有一种技术架构占据绝对主导地位。2017年,第一批存内计算公司兴起,目前存内计算中有一些技术已经可以落地,需要产业界加大投入,研发质量过关的产品。

“存内计算本身也有一个类似摩尔定律的发展过程,包括代工厂针对存内计算专用的工艺提升。其次是先进的材料,目前能够量产的存内计算存储器中,Flash和SRAM新型存储器更适合做存内计算,需要更多在新型存储器件上的研究。另外,存内计算从算法到供应链生态上也需要产学研结合,相互融合促进发展。” 刘洪杰说。

作为多年来DRAM市场份额的冠军,三星于2021年推出了结合DRAM的高带宽内存-内存内处理 (HBM-PIM),将AI计算能力引入内存。通过将经过DRAM优化的 AI 引擎置于每个存储子单元内,将处理能力直接引入到数据的存储位置,从而实现并行处理并尽可能减少数据移动。相较三星此前的高带宽内存方案,新架构能够提供超过两倍的系统性能,并降低 70% 以上的能耗。

英特尔的神经拟态计算芯片Loihi也采用了存算一体的架构,使之更加容易扩展。Loihi芯片的裸片包含128个小核,每个核里面模拟1024个神经元的计算结构,每个神经元又有1000个突触连接,这意味着768个芯片连接起来可以构建接近1亿神经元的系统。

国内聚焦存算一体芯片的企业则大多采用SRAM(静态随机存取存储器)和Flash路线。

九天睿芯基于“模拟特征提取+模数混合电荷域SRAM”架构实现存内计算,第一颗感存算一体芯片ADA100于2021年回片。后摩智能第一代芯片基于SRAM、第二代芯片基于PRAM。苹芯科技的两款产品也基于28nm SRAM。

知存科技主要采用嵌入式Flash工艺,于2020年发布第一代存算一体芯片产品WTM1001,2022年实现存算一体SoC芯片WTM2101量产并落地应用。

“近年来,随着新兴非易失存储器的发展,国内开始出现做存算一体大算力的公司,同时不断有新玩家涌入。但距离大规模应用,还有约10年的时间,从工艺、材料、算法、工具链到生态,都需要产业界和学术界的不断投入与共同推进。”王绍迪说。

产品性能和行业生态有待升级

虽然存算一体芯片的技术前景和应用场景逐渐明晰,但现阶段存算一体芯片还没有实现规模化的量产和部署,产品性能和产业生态有待进一步的提升和完善。

在性能方面,存算一体芯片还有较大的提升空间。刘洪杰表示,存算一体芯片还需要从三个方向提升性能。一是工艺迭代。随着自动驾驶等应用场景算力需求的提高,后摩尔时代存算一体芯片需要紧跟工艺迭代的红利,进一步提高能效比、面效比。二是提升精度,更多诸如飞行器航姿估计等对运算精度有较高要求的应用对存算一体架构的精度提出了一定的挑战。三是算法适配,在更广阔的消费领域,AI应用呈现碎片化的趋势,带来了算法模型的多样化,为适应应用落地需求,存算一体仍需进一步扩充计算架构的适配能力。

以九天睿芯为例,接下来将从工艺、架构等维度继续深化模数混合存算一体芯片的开发部署。据悉,九天睿芯规划了从55nm到6nm的产品路线,55nm产品主要面向TinyML(采用资源受限低功耗微控制器实施机器学习)等低功耗唤醒场景;22nm产品面向AR/VR SLAM(即时定位与地图创建)协处理、移动机器人、ADAS等场景;6nm主打面向联邦学习(带有安全加密技术的机器学习框架)、元宇宙、空间AI等应用。

此外,存算一体芯片需要强化上下游协同以加速产业化进程。王绍迪指出,存算一体芯片要实现大规模的量产、应用,涉及到上下游产业链的共同配合。包括行业标准化,以更好地实现产品落地;生态的建立,以拓展更多的应用场景。

在冯诺依曼架构中,计算和存储功能分别由中央处理器和存储器完成。而处理器在跟随摩尔定律逐年提升性能的过程中,将对制程工艺不敏感的存储器甩在了后面,两者的性能差距形成了“存储墙”。相比之下,存算一体能够避免数据来回搬运所造成的功耗损失和时间延迟。在AI技术不断释放数据洪流和算力场景需求的大趋势下,存算一体芯片越来越受到产业界和资本市场的关注。

绕过存储墙是AI时代刚需

早在1969年,斯坦福研究所的William Kautz就提出了存算一体的概念。Kautz提出在芯片的存储单元中加入逻辑电路,并将多个单元连接起来组成阵列,这样能够打造更加灵活、速度更快、耗能更低的数字电路,以更好地适应当时大规模集成电路的需求。然而,早期的存算一体研究并没有取得明显的突破,以冯诺依曼架构为蓝本、按照摩尔定律的步伐提升芯片性能,逐渐成为产业界的共识。

但近几年来,存算一体又回到了业界的视野,并被视为重要的技术方向。

知存科技创始人兼CEO王绍迪向《中国电子报》指出,过去几十年是摩尔定律快速发展的时期,加上开发新的架构需要高昂的投入,因此在摩尔定律还能往下走的时候,产业界对存算一体这类架构创新的需求还不高。但近十年以来,算力需求的增长使存储墙的问题越来越凸显。

“到2010年以后进入后摩尔时代,行业内日益增长的算力需求和几乎走到极限的摩尔定律之间越来越突出的矛盾已经成为人工智能发展的巨大瓶颈。因此,能解决存储墙问题的存算一体技术受到了越来越多的关注,近几年在产业界得到了非常快速的发展。”王绍迪说。

尤其在2016年人工智能Alpha Go在围棋对弈中战胜世界冠军李世石之后,以深度学习为代表的统计学习理论与方法促动了整个人工智能行业的发展。OpenAI的分析显示,自 2012 年以来,人工智能训练任务中使用的算力每 3.5 个月翻一倍。计算需求的突飞猛进,对算力芯片的效能提出了更高的要求和新的挑战。

从2013到2019年AI算力实现了30万倍的提升

九天睿芯董事长兼CEO刘洪杰向《中国电子报》表示,在冯诺依曼架构中,处理器从处理单元外的存储器提取数据,搬运时间往往是运算时间的成百上千倍。

“深度学习加速的最大挑战就是数据在计算单元和存储单元之间频繁的移动,市场急需可实现超高能效并且可以快速迭代的智能计算芯片来满足日新月异的市场变化。我们推出的新型类脑计算的存内计算体系架构就是面向AI发展的算力瓶颈,核心技术是解决AI算力能效比偏低的核心刚性需求。算力堆叠带来能耗问题,存算一体就是很好的解决方案。”刘洪杰说。

多种技术架构待产学研共同探索

面向智能化时代的算力需求和计算服务业态变革,英特尔、三星等IDM厂商和新锐的算力芯片厂商都在探索存算一体芯片,并衍生出不同的架构和技术路线。

刘洪杰表示,目前全球存算一体仍处于蓬勃发展阶段,没有一种技术架构占据绝对主导地位。2017年,第一批存内计算公司兴起,目前存内计算中有一些技术已经可以落地,需要产业界加大投入,研发质量过关的产品。

“存内计算本身也有一个类似摩尔定律的发展过程,包括代工厂针对存内计算专用的工艺提升。其次是先进的材料,目前能够量产的存内计算存储器中,Flash和SRAM新型存储器更适合做存内计算,需要更多在新型存储器件上的研究。另外,存内计算从算法到供应链生态上也需要产学研结合,相互融合促进发展。” 刘洪杰说。

作为多年来DRAM市场份额的冠军,三星于2021年推出了结合DRAM的高带宽内存-内存内处理 (HBM-PIM),将AI计算能力引入内存。通过将经过DRAM优化的 AI 引擎置于每个存储子单元内,将处理能力直接引入到数据的存储位置,从而实现并行处理并尽可能减少数据移动。相较三星此前的高带宽内存方案,新架构能够提供超过两倍的系统性能,并降低 70% 以上的能耗。

英特尔的神经拟态计算芯片Loihi也采用了存算一体的架构,使之更加容易扩展。Loihi芯片的裸片包含128个小核,每个核里面模拟1024个神经元的计算结构,每个神经元又有1000个突触连接,这意味着768个芯片连接起来可以构建接近1亿神经元的系统。

国内聚焦存算一体芯片的企业则大多采用SRAM(静态随机存取存储器)和Flash路线。

九天睿芯基于“模拟特征提取+模数混合电荷域SRAM”架构实现存内计算,第一颗感存算一体芯片ADA100于2021年回片。后摩智能第一代芯片基于SRAM、第二代芯片基于PRAM。苹芯科技的两款产品也基于28nm SRAM。

知存科技主要采用嵌入式Flash工艺,于2020年发布第一代存算一体芯片产品WTM1001,2022年实现存算一体SoC芯片WTM2101量产并落地应用。

“近年来,随着新兴非易失存储器的发展,国内开始出现做存算一体大算力的公司,同时不断有新玩家涌入。但距离大规模应用,还有约10年的时间,从工艺、材料、算法、工具链到生态,都需要产业界和学术界的不断投入与共同推进。”王绍迪说。

产品性能和行业生态有待升级

虽然存算一体芯片的技术前景和应用场景逐渐明晰,但现阶段存算一体芯片还没有实现规模化的量产和部署,产品性能和产业生态有待进一步的提升和完善。

在性能方面,存算一体芯片还有较大的提升空间。刘洪杰表示,存算一体芯片还需要从三个方向提升性能。一是工艺迭代。随着自动驾驶等应用场景算力需求的提高,后摩尔时代存算一体芯片需要紧跟工艺迭代的红利,进一步提高能效比、面效比。二是提升精度,更多诸如飞行器航姿估计等对运算精度有较高要求的应用对存算一体架构的精度提出了一定的挑战。三是算法适配,在更广阔的消费领域,AI应用呈现碎片化的趋势,带来了算法模型的多样化,为适应应用落地需求,存算一体仍需进一步扩充计算架构的适配能力。

以九天睿芯为例,接下来将从工艺、架构等维度继续深化模数混合存算一体芯片的开发部署。据悉,九天睿芯规划了从55nm到6nm的产品路线,55nm产品主要面向TinyML(采用资源受限低功耗微控制器实施机器学习)等低功耗唤醒场景;22nm产品面向AR/VR SLAM(即时定位与地图创建)协处理、移动机器人、ADAS等场景;6nm主打面向联邦学习(带有安全加密技术的机器学习框架)、元宇宙、空间AI等应用。

此外,存算一体芯片需要强化上下游协同以加速产业化进程。王绍迪指出,存算一体芯片要实现大规模的量产、应用,涉及到上下游产业链的共同配合。包括行业标准化,以更好地实现产品落地;生态的建立,以拓展更多的应用场景。

据王绍迪介绍,接下来知存科技会从产品和生态层面进行升级,在初步构建存算一体开发小生态的基础上,随着芯片算力、计算容量、计算速度的不断增加,打造更丰富更便捷的开发工具链,稳定架构、打磨标准化产品、拓宽应用场景逐渐从端侧发展到边缘测或云端。

电子元件展,2022电子元件展览会,上海电子元件展,电子元器件展,上海电子元器件展会,上海电子元件展会,上海电子元器件展,电子元器件展览会,2022电子元器件展览会,2022上海电子展,2022半导体展览会,上海半导体展,上海传感器展览会,2022传感器展览会,2022电子设备展览会,上海电子设备展,上海电子材料展,上海芯片展,2022芯片展览会,2022第十届中国(上海)国际电子元器件展览会